**Bachelor Informatica**

# **Thread-Oriented Program algebra**

Author: Sebastian Melzer

Supervisors: Alban Ponse and Inge Bethke

### Context

- Basic Thread Algebra (BTA)

- Syntax to define the **behaviour** of sequential programs

- Program Algebra (PGA)

- □ Simple program notation (language)

- Uses BTA to define its behaviour

- Semigroup C

- Alternative to PGA

- No directional bias

- Thread-Oriented Program algebra (TOP)

- □ Variation of C

- Strong correlation with BTA

## **Basic Thread Algebra**

- Used to describe the behaviour of sequential programs

- Arbitrary set of actions  $A = \{a, b, c, ...\}$

- All actions yield true or false on execution

- BTA expressions are called threads  $\{P, Q, R, \dots\}$

- □ The *deadlock* constant D

- The termination constant S

- □ The postconditional composition operator  $P \subseteq a \trianglerighteq Q$

- The *action prefix* operator  $a \circ P$  is shorthand for  $P \subseteq a \trianglerighteq P$

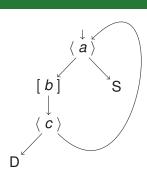

$$P_1 = P_2 \le a \ge P_4$$

$P_2 = b \circ P_3$

$P_3 = P_5 \le c \ge P_1$

$P_4 = S$

$P_5 = D$

## **TOP syntax**

### Instruction sequence

A finite sequence of instructions:  $u_1$ ;  $u_2$ ; ...;  $u_n$

#### Instructions

- *Basic* instructions /a and  $\setminus a$  for  $a \in A$

- *Jump* instructions /#k and  $\backslash\#k$  for  $k \in \mathbb{N}$

- *Test* instructions +a and -a for  $a \in A$

- The *termination* instruction!

- The *abort* instruction #

### **TOP semantics**

For an instruction sequence  $X = u_1; \ldots; u_n$ , the thread extraction operator  $|X|_i$  returns the regular thread that is modelled by  $u_i$  in Χ.

#### Definition

Definition

$$|X|_{i} = \begin{cases} a \circ |X|_{i+1} & \text{if } u_{i} = /a, \\ |X|_{i+k} & \text{if } u_{i} = /\#k, \\ |X|_{i-1} \le a \ge |X|_{i+1} & \text{if } u_{i} = +a, \end{cases}$$

$$\vdots \quad \text{similar equations for } \backslash a, \backslash \#k, -a$$

$$D \quad \qquad \text{if } u_{i} = \#,$$

$$S \quad \qquad \text{if } u_{i} = \#.$$

$$X = /#2; !; +a; -b; #$$

$$|X|_1 = |X|_3$$

$|X|_2 = S$

$|X|_3 = |X|_2 \le a \ge |X|_4$

$|X|_4 = |X|_5 \le b \ge |X|_3$

$|X|_5 = D$

## On the length of TOP instruction sequences

#### (Q1) Instruction sequence to thread

How many linear equations are required to define the behaviour expressed by an instruction sequence of length *n*?

#### (Q2) Thread to instruction sequence

How many instructions are required to express the behaviour defined by a linear specification of *n* equations?

## Q1: Instruction sequence to thread

#### Theorem

The behaviour expressed by a TOP instruction sequence of length n can be defined by a linear specification of n+1 equations.

#### Proof.

- 1. There are three base cases:

- Basic or test instruction results in 2 equations

- □ Jump, abort, or termination instruction results in 1 equation

- 2. To add an instruction to the sequence *X* we need at most 1 extra equation.

Instruction sequence Linear specification

$$\begin{array}{c}

+a \\

P_1 = a \circ P_D \\

P_D = D

\end{array}$$

$$+a; /b \\

P_1 = P_D \unlhd a \trianglerighteq P_2 \\

P_2 = b \circ P_D \\

P_D = D$$

$$P_1 = P_D \unlhd a \trianglerighteq P_2 \\

P_2 = b \circ P_3 \\

P_3 = S \\

P_D = D$$

### Q2: Thread to instruction sequence

#### Theorem

The minimum length of TOP instruction sequences required to model all regular threads of n states is  $3n - \lceil \frac{n}{2} \rceil$ .

### Proof.

- 1. Showing that 3n is an upper bound is trivial

- 2. For a constant (S or D) 2 instructions can be saved.

- 3. When a state is directly reachable from two other states (or twice from the same state) an instruction can be saved.

- $\Box$  There are at least  $\lceil \frac{n}{2} \rceil$  such cases if no state is constant.

## On the expressiveness of TOP

### (Q3) Size of jumps counters

Are arbitrarily large jump counters required in both directions to model all regular threads?

### Q3: Size of jump counters

### Theorem

Let  $\mathsf{TOP}^{\leq k}$  be the subset of  $\mathsf{TOP}$  that includes all instructions except forward jump instructions with a jump counter greater than  $k \in \mathbb{N}^+$ .

$\mathsf{TOP}^{\leq k}$  instruction sequences cannot model all regular threads for any k.

### Proof.

Assuming the opposite results in a contradiction.

### **TOP in 2 dimensions**

### Instruction plane

A matrix of instructions:

$$X = \begin{bmatrix} u_{1,1} & \cdots & u_{1,n} \\ \vdots & \ddots & \vdots \\ u_{m,1} & \cdots & u_{m,n} \end{bmatrix}$$

.

#### Instructions

- *Basic* instructions /a,  $\setminus a$ ,  $\uparrow a$ ,  $\downarrow a$  for  $a \in A$

- *Jump* instructions /#k,  $\backslash \#k$ ,  $\uparrow \#k$ ,  $\downarrow \#k$  for  $k \in \mathbb{N}$

- *Test* instructions +a, -a,  $\updownarrow +a$ ,  $\updownarrow -a$  for  $a \in A$

- The *termination* instruction!

- The *abort* instruction #

### **Properties of TOP**<sub>2</sub>

### (Q4) Expressiveness TOP versus TOP<sub>2</sub>

Does the second dimension of TOP<sub>2</sub> add expressiveness in comparison to TOP?

### (Q5) Size of jumps counters in 2D

Are arbitrarily large jump counters required in TOP<sub>2</sub> to model all regular threads?

### Q4: Expressiveness TOP versus TOP<sub>2</sub>

#### Theorem

TOP instruction sequences and TOP<sub>2</sub> instruction planes are equally expressive.

### Proof.

- 1. An instruction sequence can be transformed into an instruction plane.

- 2. An instruction plane can be transformed into an instruction sequence.

## Q5: Size of jumps counters in 2D

#### Theorem

Let  $TOP_2^{\leq 2}$  be the subset of  $TOP_2$  that does not contain jump instructions with a jump counter greater than 2.

$\mathsf{TOP}_2^{\leq 2}$  instruction sequences can model all regular threads.

#### Proof.

- 1. If *P* is a regular thread you can draw a 2-dimensional representation of *P*.

- 2. The image can be discretised into an instruction plane which models *P*.

$$P_1 = P_2 \le a \ge P_3$$

$$P_2 = b \circ P_3$$

$$P_3 = P_4 \le c \ge P_5$$

$$P_4 = d \circ P_2$$

$$P_5 = e \circ P_2$$

```

↓#1

+a

↓#1

J#1

↓#1

\#1

↓#1

\#2

\#1

↓b

/#1

↓#1

↑#1

\#1

J#1

↓#1

1#1

/#1

/#1

/#1

↓#1

1#1

\#1

/#1

↑#1

↓#1

↓#1

1#1

+c

↑#1

↓#1

\#1

/#1

↓#1

†#1

↑#1

↓#1

↓#1

†#1

1#1

/#1

↑#1

\#1

```

### **Discussion**

### Summary

- TOP to BTA: n instructions  $\rightarrow n + 1$  states

- BTA to TOP: n states  $\rightarrow 3n \lceil \frac{n}{2} \rceil$  instructions

- TOP and TOP<sub>2</sub> are equally expressive

- Arbitrarily large jumps necessary in TOP but not in TOP<sub>2</sub>

### **Questions?**

## Why is TOP thread-oriented?

| Language        | Instruction sequence                                | Thread                                                                                                  |

|-----------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| PGA<br>C<br>TOP | $+a; u_1; u_2$<br>$/+a; u_1; u_2$<br>$u_1; +a; u_2$ | $ u_1  \leq a \geq  u_2 $ |

## Why is 3n an upper bound?

Transforming  $\{P_1 = t_1, \dots, P_n = t_n\}$  into  $X = X_1; \dots; X_n$  results in at most three instructions per  $X_i$ .

$$X_{i} = \begin{cases} ! & \text{if } P_{i} = S, \\ \# & \text{if } P_{i} = D, \\ \mathcal{J}(P_{j}); +a; \mathcal{J}(P_{k}) & \text{if } P_{i} = P_{j} \leq a \geq P_{k}, \end{cases}$$

where  $\mathcal{J}(P_j)$  is a jump instruction to  $X_j$ .

$$P_{1} = P_{2} \unlhd a \trianglerighteq P_{3}$$

$X_{1} = \mathcal{J}(P_{2}); +a; \mathcal{J}(P_{3})$

$P_{2} = D$   $X_{2} = \#$

$P_{3} = b \circ P_{4}$   $\to$   $X_{3} = \mathcal{J}(P_{4}); +b; \mathcal{J}(P_{4})$

$P_{4} = S$   $X_{4} = !$

$X = /\#3; +a; /\#3; \#; /\#3; +b; /\#1; !$

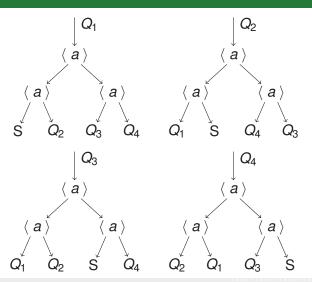

# Why are there at least $\lceil \frac{n}{2} \rceil$ cases?

If we consider only non-constant states:

- 1. Each state has two *outbound arcs*.  $(P \subseteq a \supseteq Q)$

- 2. If there are n states, there are 2n arcs in total.

- 3. Each state that has a pair of inbound arcs is such a case.

- 4. Minimising this number of pairs results in  $\lceil \frac{n}{2} \rceil$ .

### Example

If n = 6 there at least 3 such pairs.

| State         | $P_1$ | $P_2$    | $P_3$ | $P_4$    | $P_5$ | $P_6$ |

|---------------|-------|----------|-------|----------|-------|-------|

| Outbound arcs | 2     | 2        | 2     | 2        | 2     | 2     |

| Inbound arcs  | 1     | <u>3</u> | 1     | <u>3</u> | 1     | 3     |